- COMPILE BOOT.ELF HOW TO

- COMPILE BOOT.ELF INSTALL

- COMPILE BOOT.ELF SERIAL

- COMPILE BOOT.ELF DRIVERS

- COMPILE BOOT.ELF DRIVER

the selected configuration file: configs/stm32mp*_defconfig. options defined in Kconfig files (CONFIG_ compilation flags). Kbuild infrastructure (as in Linux Kernel, you can use make menuconfig in U-Boot). The U-Boot binary configuration is based on pass the control to the Linux kernel (or to another target application). COMPILE BOOT.ELF INSTALL

install the secure monitor (optional) or. load and check images (such as kernel, device tree and ramdisk). Execution of the boot command (by default bootcmd=CONFIG_BOOTCOMMAND):įor example, execution of the command bootm to:. Command execution through autoboot (CONFIG_AUTOBOOT) or console shell. Post-relocation initialization:(common/board_r.c): initialization of all the drivers. Relocation: copy of the code to the end of DDR memory. Pre-relocation initialization (common/board_f.c): minimal initialization (such as CPU, clock, reset, DDR and console) running at the CONFIG_SYS_TEXT_BASE load address. U-Boot executes the following main steps in DDR memory: USB: host (mass storage) or device (DFU stack). Display: LCD, HDMI, BMP for splashcreen. It supports the following features and commands:. It manages several internal and external devices such as NAND and NOR Flash memories, Ethernet and USB. It loads the kernel into RAM and gives control to the kernel. COMPILE BOOT.ELF SERIAL

It features a simple command line interface (CLI), allowing users to interact over a serial port console. U-Boot is the second-stage bootloader (SSBL) of boot chain for STM32 MPU platforms. loading and execution of U-Boot (or Kernel in Falcon mode : README.falcon ).Ģ.2 U-Boot: SSBL 2.2.1 U-Boot description. COMPILE BOOT.ELF DRIVERS

board_init_r(): initialization of the other drivers activated in the SPL device tree.

configuration of heap in DDR memory (CONFIG_SPL_SYS_MALLOC_F_LEN).

COMPILE BOOT.ELF DRIVER

board_init_f(): driver initialization including DDR initialization (mininimal stack and heap: CONFIG_SPL_STACK_R_MALLOC_SIMPLE_LEN). SPL executes the following main steps in SYSRAM: There is no workaround for these limitations. SCMI support for clock and reset (not compatible with latest Linux kernel device tree). limited features (STM32CubeProgrammer / boot from NAND Flash memory). However, several known limitations have been identified when SPL is used in conjunction with the minimal secure monitor provided within U-Boot for basic boot chain. SPL is provided only as an example of the simplest FSBL with the objective to support upstream U-Boot development. SPL cannot be used for product development. It loads the SSBL (U-Boot) into the DDR memory. It performs the initial CPU and board configuration (clocks and DDR memory). It is a small binary (bootstrap utility) generated from the U-Boot source and stored in the internal limited-size embedded RAM.

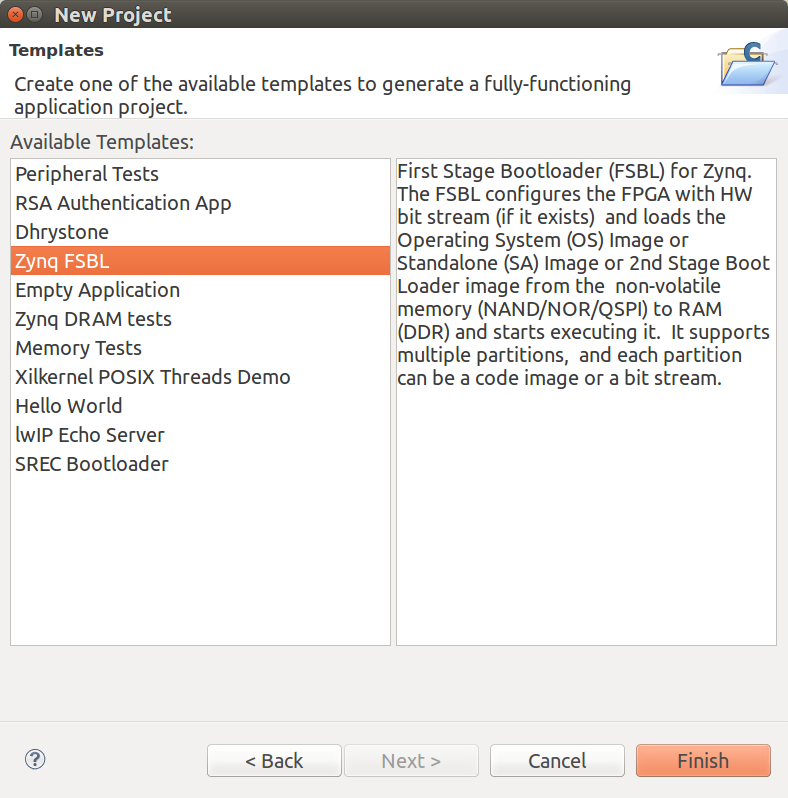

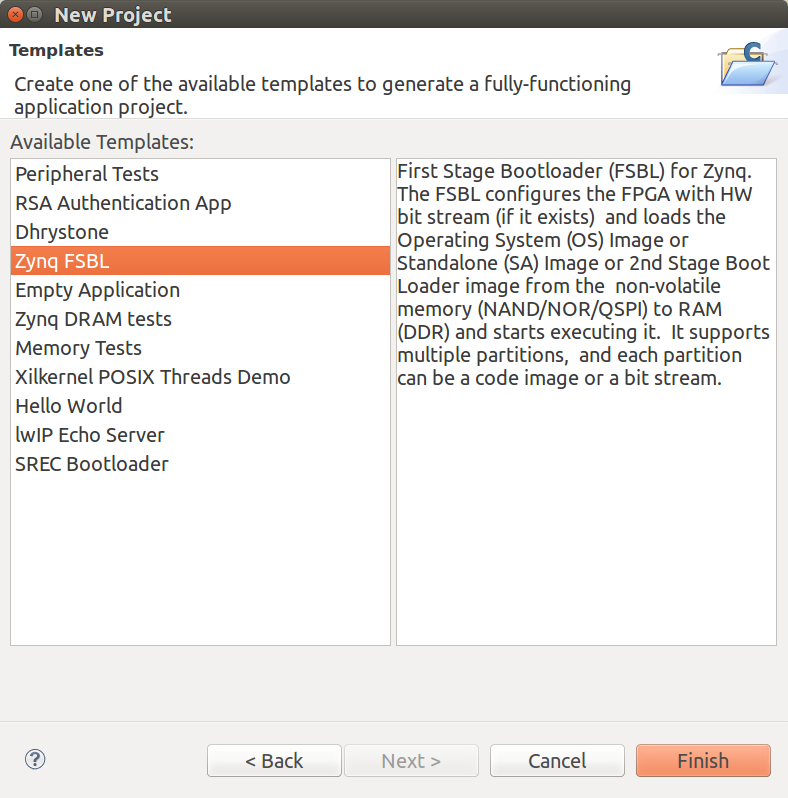

There are several ways to retrieve the U-Boot source code.The U-Boot SPL or SPL is an alternate first stage bootloader (FSBL). $ export CROSS_COMPILE=aarch64-linux-gnu-ģ. Then, configure your environment to access the Linaro cross compiler. Download and extract the Linaro toolchain. Intel SoC FPGA EDS 19.3 Pro Edition (only if planning to use U-Boot source code from SoC FPGA EDS)Ģ.Host PC running Linux ( Ubuntu 16.04 LTS).Otherwise the pre-compiled boot loader can be used as-is. This may be needed in case any changes are made to the boot loader.

COMPILE BOOT.ELF HOW TO

This page presents how to re-compile the Stratix 10 SoC U-Boot First Stage Boot Loader (FSBL) and Second Stage Boot Loader (SSBL).

Terasic Stratix 10 SoC Board : DE10-Pro.

Terasic Stratix 10 SoC Board : Apollo S10 SoM. REFLEX CES COMXpressSX Stratix 10 Module. Terasic DE1-SoC Development and Education Board. Solectrix SMARC compliant System-on-Module. Networked Pro-Audio FPGA SoC Development Kit by Coveloz. Mpression Borax SOM Module and Development Kit by Macnica. Mpression Sodia Evaluation Board by Macnica. Mpression Helio SoC Evaluation Kit by Macnica. Altera Cyclone V SoC Development Platform. Critical Link MitySOM-5CSx Development Kit. Arrow SoCKit User Manual - November 2019 Edition. Arrow SoCKit User Manual - July 2017 Edition. Terasic Arria10 SoC Board : HAN Pilot Platform. Nallatech 510T compute acceleration card with Intel Arria 10 FPGA. ALARIC Instant DevKit ARRIA 10 SoC FMC IDK by REFLEX CES. Nallatech 385A-SoC Accelerator Card with Arria 10 FPGA. Nallatech 385A - Arria 10 FPGA Network Accelerator Card.

0 kommentar(er)

0 kommentar(er)